【AscendC】算子调用API的对齐问题

在AscendC算子开发的过程中,存在一个tiling下发的概念,如果将tiling的tileNum改的比较大,那么会出现报错,实验结果如下:

| tileNum | 64 | 128 | 256 |

|---|---|---|---|

| 1(BufferNum) | T | T | F |

| 2(BufferNum) | T | F | F |

在NPU侧调试的信息无法输出,如果发生报错也不知道原因。

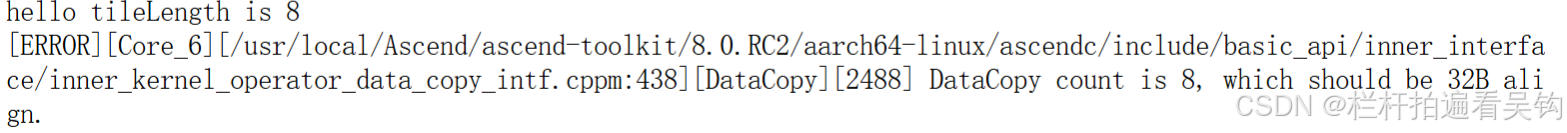

遂使用CPU侧进行模拟,报错信息如下:

可以看到,当我指定BufferNum为2且tileNum为128时,会发生报错,提示数据无法对齐,此时一个tiling的计算是8个数据,由于是half类型,即2B大小,因此每次进行拷贝的数据量总计16B,而规定的数据对齐方式为32B,因此会发生报错,得到的结果也会存在错误信息。