Xilinx远程固件升级(二)——STARTUPE2原语的使用

通过(一)可以看出,对于远程固件升级实际上是通过调用flash不同区域的bit实现,通过golden image和update image共同保障了系统的稳定性。在项目中如果将flash的时钟直接绑定FPGA后进行约束,在综合编译时是无法通过的。这是因为CCLK_0管脚内部被占用,因此,在设计时需要通过其它方式来对该引脚进行配置,以KC705开发板为例,根据Xilinx UG470文档可以得出,可以使用STARTUPE2原语来对CCLK_0时钟进行获取和配置时钟。

STARTUPE2 #(

.PROG_USR(“FALSE”), // Activate program event security feature. Requires encrypted bitstreams.

.SIM_CCLK_FREQ(0.0) // Set the Configuration Clock Frequency(ns) for simulation.

)

STARTUPE2_inst (

.CFGCLK(), // 1-bit output: Configuration main clock output

.CFGMCLK(), // 1-bit output: Configuration internal oscillator clock output

.EOS(), // 1-bit output: Active high output signal indicating the End Of Startup.

.PREQ(), // 1-bit output: PROGRAM request to fabric output

.CLK(0), // 1-bit input: User start-up clock input

.GSR(0), // 1-bit input: Global Set/Reset input (GSR cannot be used for the port name)

.GTS(0), // 1-bit input: Global 3-state input (GTS cannot be used for the port name)

.KEYCLEARB(1), // 1-bit input: Clear AES Decrypter Key input from Battery-Backed RAM (BBRAM)

.PACK(1), // 1-bit input: PROGRAM acknowledge input

.USRCCLKO(outSpiClk), // 1-bit input: User CCLK input

// For Zynq-7000 devices, this input must be tied to GND

.USRCCLKTS(0), // 1-bit input: User CCLK 3-state enable input

// For Zynq-7000 devices, this input must be tied to VCC

.USRDONEO(1), // 1-bit input: User DONE pin output control

.USRDONETS(1) // 1-bit input: User DONE 3-state enable output

);

| 引脚名称 | 类型 | 描述 |

|---|---|---|

| CLK | 输入 | 用户启动时钟引脚。来自驱动设备启动序列时钟的FPGA逻辑的输入。为启动序列提供用户定义的CCLK。Spartan 7 7S6和7S15设备不支持启动序列的用户定义CCLK(ITSTREAM.STARTUP.STARTUPCLK属性的UserClk值)。 |

| GSR | 输入 | 一般将其设置为低电平表示禁用 |

| GTS | 输入 | 全局三态引脚,作用是将配置库以外的用户I/O都配置成高阻态,一般情况将其设置为低电平。 |

| KEYCLEARB | 输入 | 从电池支持的RAM中清除AES解密器秘钥。FPGA结构的低电平输入。当数据表中的TPROGRAM延时保持低电平时,该引脚会从电池备份RAM(BBRAM)中擦除解密秘钥的内容。 |

| PACK | 输入 | PROGRAM_B或JPROGRAM确认。FPGA逻辑的输入,用于“确认”PROGRAM_B信号的断言,并允许PROGRAM_B状态机的其余部分继续重置FPGA。仅当设置了PROG_USR属性时,此引脚才启用。 |

| PREQ | 输出 | FPGA逻辑需要PROGRAM_B脉冲或JPROGRAM。FPGA逻辑的输出。此引脚是PROGRAM_B状态机重置设备的“请求”,允许PROGRAM_B请求被门控,直到设计处于可以完成重置的状态。仅当设置了PROG_USR属性时,此引脚才启用。 |

| USRCCLKO | 输入 | CCLK引脚。配置后,FPGA逻辑的输入,将定制的逻辑生成时钟频率驱动到FPGA CCLK引脚上。可用于外部配置后访问SPI闪存设备。更多详细信息请参见USRCCLKO。 |

| USRCCLKTS | 输入 | 用户CCLK三态启用CCLK引脚。FPGA逻辑的高电平输入,在配置后使用时将FPGA CCLK引脚置于高Z状态。对于大多数应用,此引脚应系低。 |

| USRDONEO | 输入 | 完成引脚输出值。连接到FPGA DONE引脚的FPGA逻辑的输入。 |

| USRDONETS | 输入 | 用户完成了DONE引脚的三态启用。FPGA逻辑的高电平输入,使DONE进入高阻状态。通常设置为低电平用来启用DONE。 |

| CFGCLK | 输出 | 配置逻辑主时钟输出。FPGA逻辑的输出。从专用内部环形振荡器输出时钟信号,其中典型频率由比特流配置速率选项定义。输出仅在配置期间以及启用持久性的主模式下处于活动状态。 |

| CFGMCLK | 输出 | 配置内部振荡器时钟输出。FPGA逻辑的输出。从专用内部环形振荡器输出典型频率为65 MHz的时钟信号。 |

| EOS | 输出 | 启动结束。高电平输出将EOS标志回声到FPGA逻辑中。可以用作指示FPGA已准备好运行的复位信号。 |

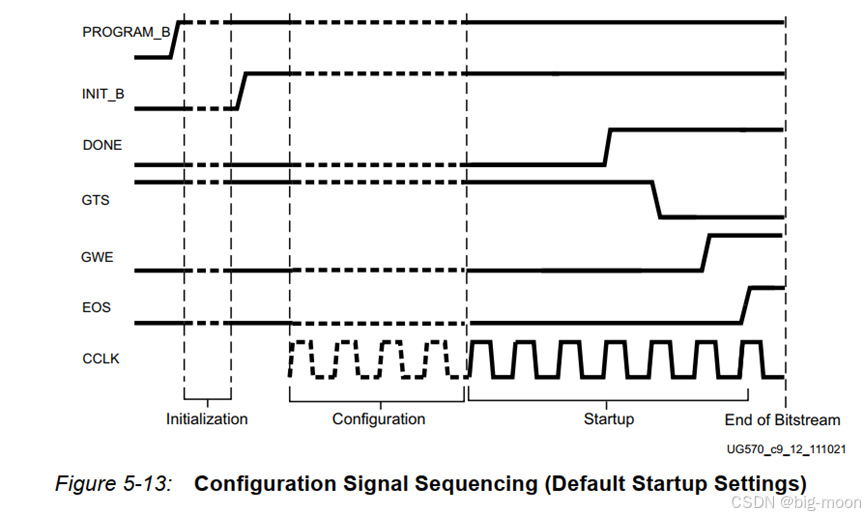

部分信号的默认时序图如图1所示。

图1 STARTUPE2部分引脚时序图

如果是通过该原语进行Flash的控制,可直接复制本文中原语的设置,仅需要更新自己的时钟信号即可。