DDR Study - Basic Understanding

参考来源:https://www.sjalander.com/research/thesis/, https://www.systemverilog.io/, JESD209-4.

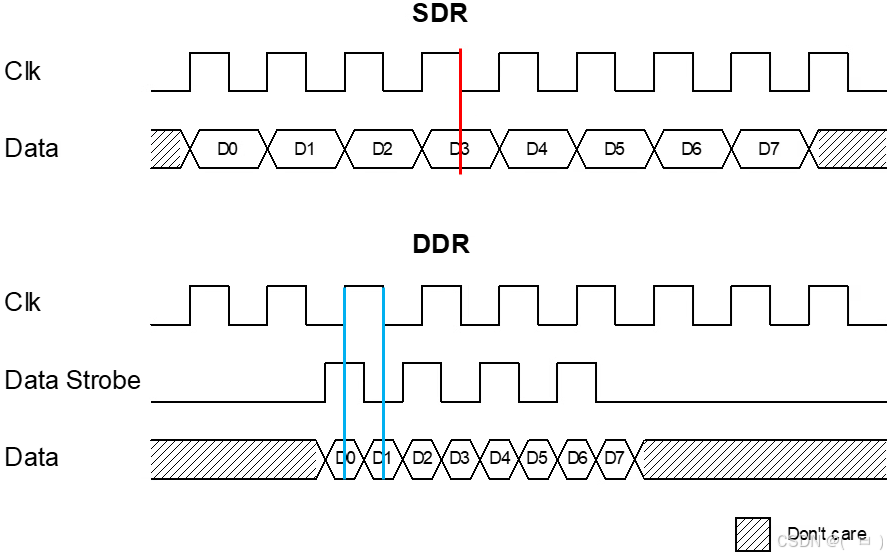

DDR vs SDR

SDR - Single Data Rate接口协议中,每个Data Bit都是在Clock信号的上升沿或者下降沿进行传输,一个Clock周期只能传输1 bit Data。

假设SDR在一个Clk上升沿驱动传输Data信号,只需要在Clk下降沿(上图红线)进行采样即可。

DDR - Double Data Rate接口协议中,支持每个Data Bit在Clock信号的上升沿和下降沿都进行传输,一个Clock周期能传输2 bit Data。

并且DDR增加了Data Strobe信号,因为DDR一个Clk周期上升下降沿都用于驱动传输Data信号(上图蓝线),所以需要额外的strobe信号采样Data数据。

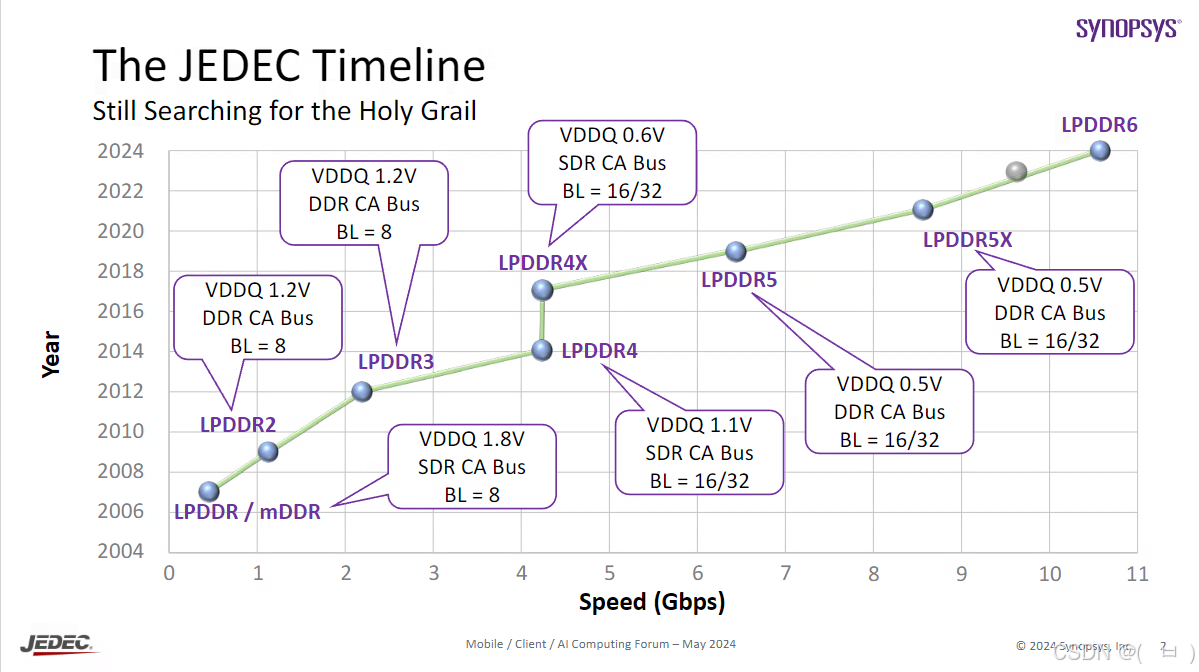

下面是Synopsys在2024年提供的一份LPDDR趋势信息:

可以看到随着LPDDR不断迭代,功耗逐渐降低,支持的带宽速率不断增加,目前已经高达10Gbps。

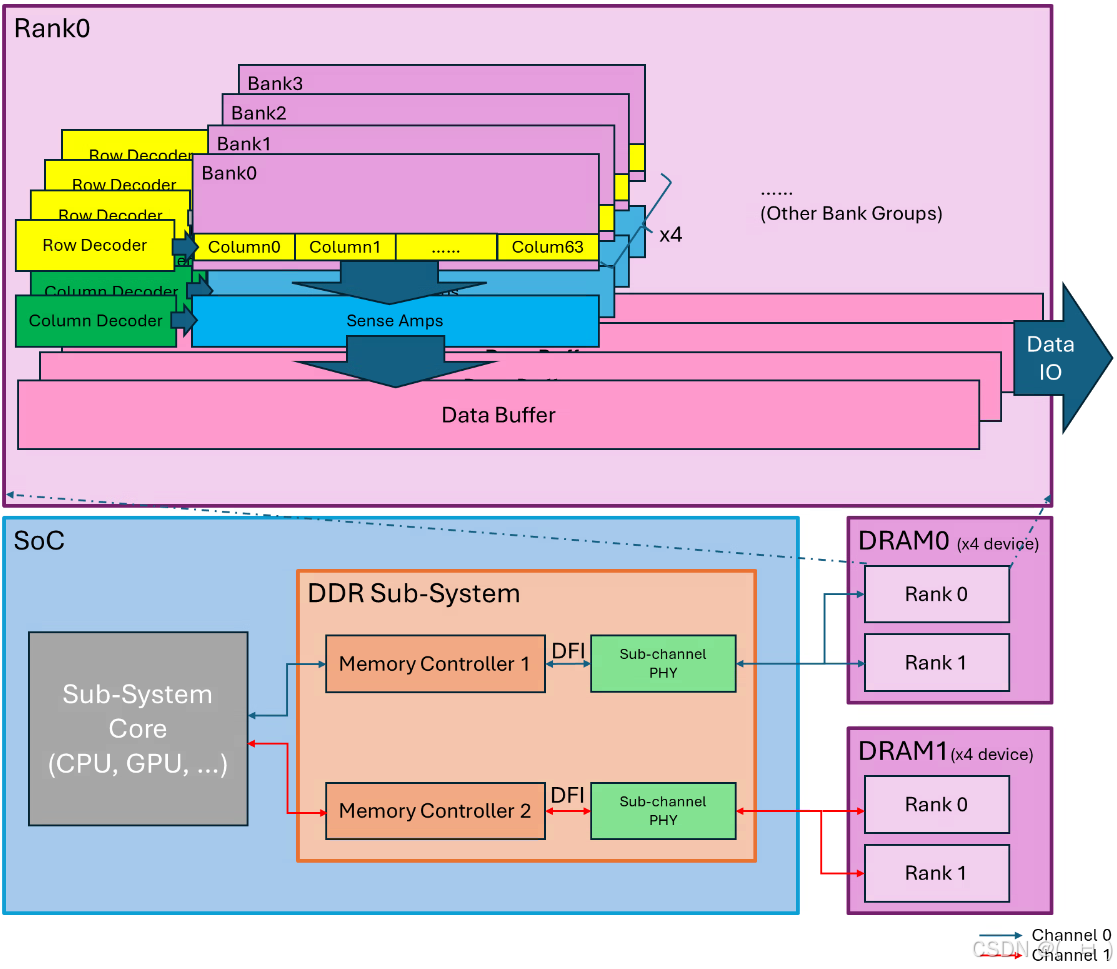

宏观视角下的DRAM

下图并不是一个标准的DRAM设计,只是对DRAM与SoC之间可能存在的关系进行粗略描述,具体细节以具体平台设计和JEDEC规范为准。

宏观视角下,常见的DRAM相关对象信息整理如下:

| Name | Description |

|---|---|

| Channel | 通道可以理解为单次传输Data Packet所使用的路径 |

| Rank | 多个Memory Bank或者Memory Bank Group的级联 |

| Bank | Memory Bank包含由Row和Column矩阵组成的Memory Cell集合体 |

| Memory Controller | 负责处理SoC的请求,通过DFI协议与PHY通信,PHY将对应的电气信号发送到DRAM |

| DIMM | Dual In-Line Memory Module, 指内存上的正反接触面和主板内存插槽的接触模块 |

| chip | 一般指物理上的一片DRAM物料贴片 |

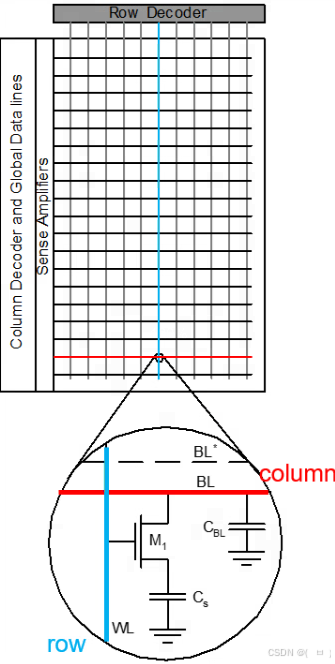

微观视角下的DRAM

下图是一个从DRAM Bank中放大的DRAM Cell,可以看到一个Cell由1个晶体管M和1个电容Cs组成。右边的电容CBL是用于控制BL - Bank Line的寄生电容。

在读写DRAM操作中,通过行选择和列选择来操作DRAM Cell,而Cell就位于行列选择线的交叉处。

电容Cs中存储的电荷量高低代表了一个Cell存储的信息。

而电容中的电荷,也会随着晶体管的开关漏电而慢慢流失。所以DRAM需要每隔一段时间进行一次刷新,对流失的电荷进行补充。

Access DRAM

正常的一次DRAM访问流程如下,以Read/Write为例:

- 用户给出需要访问的地址信息到SoC,交给Memory Controller处理。

- 地址信息经过Remapping后解析出 Channel, Rank, Bank, IO Width, Row, Column等信息并传输到DRAM端。

- RD/WR命令到DRAM段后,首先触发ACTIVATE命令,负责激活Bank Group, Bank和Row,也被称之为RAS - Row Address Strobe。

- ACTIVATE命令之后,再是激活Column,也就是CAS - Column Adress Strobe。

- 此时每个Memory的放大模块 Sens Amps会将选中的DRAM Cell中的电荷信息放大为0 (GND) / 1 (VDD) 的电平信息。

- 当需要访问同一个Bank里另一行Row或者结束访问时,需要将当前打开的Row执行PRECHARGE指令,从而把Sense Amps中的对应数据重新写回当前Row。

下面是基于JEDEC中的Read/Write时序图进行部分介绍,详细内容解析会在此专栏后续进行介绍。

Read

Read命令是DRAM发送数据到Memory Controller,每次MC都需要基于DQS信号进行采样。

所以在CAS信号传输结束后,DRAM就必须在发送DQ Data信号之前先发送DQS信号。

图中可以看到在CAS信号之后,还需要等待RL + tDQSCK + tDQSQ的时间,才出现了第一个DQ Data Bit可以采样。相关参数信息如下:

- RL - Read Latency, Read行为中在CAS指令之后直到tDQSCK之间的时间,可以在DRAM的Mode Register里配置。这段时间DRAM会激活对应的DRAM Cell并将数据传输出来。

- tDQSCK - Read访问场景下,RL之后的第一个Clock和第一个用于采样的DQS信号之间的skew,需要通过training限制在一个合理的范围内。

- tDQSQ - Read访问场景下,第一个用于采样的DQS信号和第一个DQ信号之间的skew,需要通过training限制在一个合理的范围内。

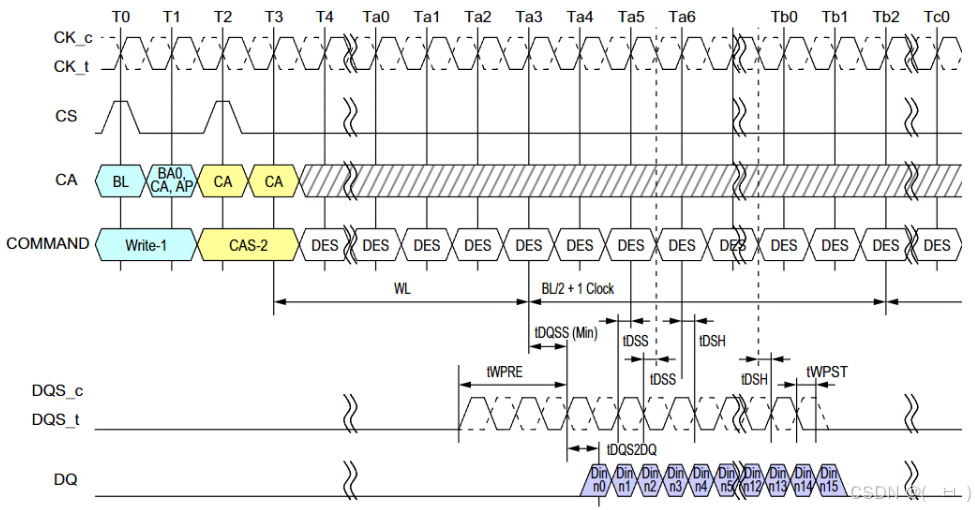

Write

Write命令是Memory Controller发送数据到DRAM,每次DRAM都需要基于DQS信号进行采样,写数据到DRAM Cell中。

所以Memory Controller也必须在发送DQ Data信号之前先发送DQS信号。

图中可以看到在CAS信号之后,还需要等待WL + tDQSS + tDQS2DQ 的时间,才出现了第一个DQ Data Bit可以采样。相关参数信息如下:

- WL - Write Latency, Write行为中在CAS指令之后直到tDQSS之间的时间,可以在DRAM的Mode Register里配置。这段时间DRAM会激活对应的DRAM Cell等待数据写入。

- tDQSS - Write访问场景下,RL之后的第一个Clock和第一个用于采样的DQS信号之间的skew,需要通过training限制在一个合理的范围内。

- tDQS2DQ - Write访问场景下,第一个用于采样的DQS信号和第一个DQ信号之间的skew,需要通过training限制在一个合理的范围内。

LPDDR4 PAD

上面的Read和Write访问时序图中提到了很多CA/CS/DQS等信号,下面基于LPDDR4的规范对这些信号线进行简单介绍:

| Symbol | Name | Type | Description |

|---|---|---|---|

| CK_t_A, CK_c_A CK_c_B, CK_t_B | Clock | Input | Clock使用差分信号 所有的地址,命令和输入控制信号都是在CK_t上升沿采样 CA信号的AC Timing参考CK信号 |

| CKE_A, CKE_B | Clock Enable | Input | CKE信号为高,会Enable Clock CKE为低,会关闭内部clock和输入缓存和输出驱动 CKE可以控制Power-Saving Mode的开关 |

| CS_A, CS_B | Chip Select | Input | 片选信号 |

| CA_A, CA_B | Command and Address | Input | Command和Address信息基于一个真值表提供 |

| ODT(ca)_A, ODT(ca)_B | CA ODT Control | Input | 控制CA信号的ODT开关 |

| DQ[15:0]_A, DQ[15:0]_B | Data Input/Output | I/O | 双向的Data总线 |

| DQS[15:0]_t_A, DQS[15:0]_c_A DQS[15:0]_t_B, DQS[15:0]_c_B | Data Strobe | I/O | DQS是双向的差分时钟信号 用于在Read和Write命令中采样Data DQS必须在Data信号到达前产生 Read命令中DQS由DRAM产生 Write命令中由Memory Controller产生 |

| DMI[1:0]_A, DMI[1:0]_B | Data Mask Inversion | I/O | DMI是双向信号 DMI为高会翻转Data Bus上的信号,为低则不影响 DMI可以用来为Write Data提供Mask功能 DMI的翻转功能和Mask功能都可以通过DRAM的Mode Register配置 |

| ZQ | Calibration Reference | Reference | 用于校准输出驱动强度和终端电阻 |

| VDDQ, VDD1, VDD2 | Power Supplies | Supply | 供电Pin,并且做了隔离来提高抗噪能力 |

| VSS, VSSQ | Ground Reference | GND | 供电的参考地端 |

| RESET_n | Reset | Input | RESET置低会重置Die上所有Channel 一个Die上只有一个RESET_n pad |

Note1: 有“_A"的信号代表适用于所有DRAM设备, “_B"代表仅适用双通道(Dual-Channel)设备。

Note2: 有“_A"和“_B"的信号都代表在双通道设备中每个通道都有独立的信号。

Note3: "_t"代表差分信号中的true (positive) 信号, "_c"代表差分信号中的complement (negative) 信号。

Note4: ODT - On Die Termination, Die上的终端电阻。目的是让DQS, DQ, DMI这些信号通过ODT消耗完,防止形成信号反射。

后话

这篇文章是DDR专栏的开始,后面会基于JEDEC标准以及实际的调试场景,慢慢整理出关于DRAM初始化,DRAM Training,DRAM信号分析等方面的内容,欢迎订阅。