FSMC

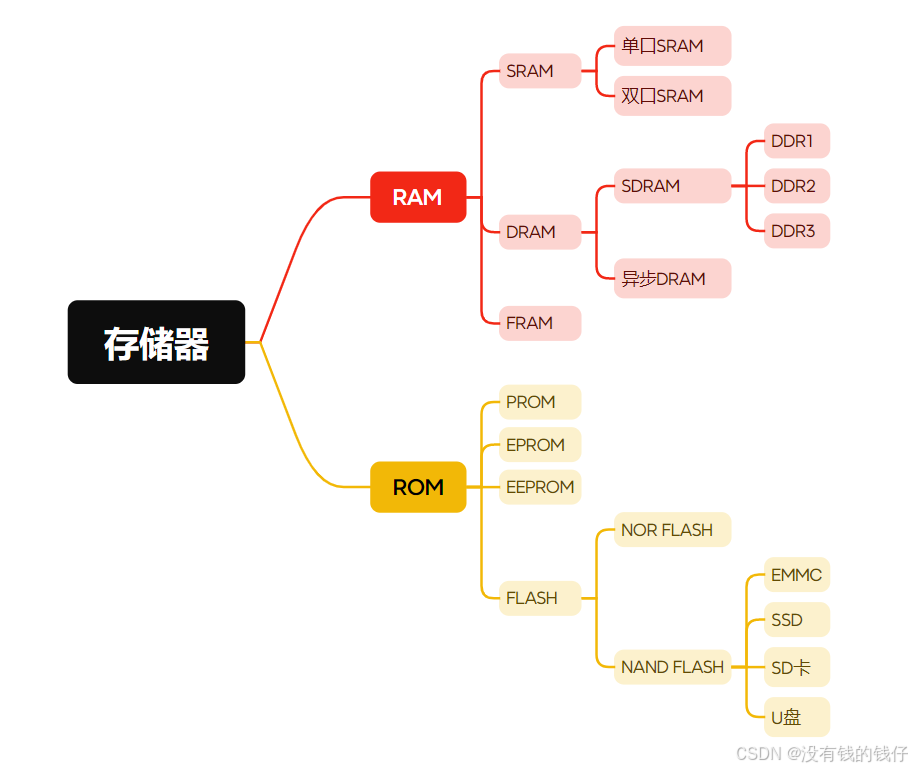

RAM ROM

RAM和ROM相比,两者的最大区别是RAM在断电以后保存在上面的数据会自动消失,而ROM不会自动消失,可以长时间断电保存。 并且RAM的速度要远远高于ROM的速度。

SRAM

SRAM 的存储单元以锁存器来存储数据,种电路结构不需要定时刷新充电,就能保持状态

DRAM

DRAM,动态随机存取存储器,需要不断的刷新,才能保存数据

SDRAM

SDRAM(Synchronous Dynamic Random Access Memory),同步动态随机存储器。同步的DRAM

DRAM可以分为同步和异步两种,这两种方式根据通讯时是否需要使用时钟信号来区分。

同步是指内存工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;

动态是指存储阵列需要不断的刷新来保证数据不丢失;

随机是指数据不是线性依次存储,而是自由指定地址进行数据读写。

SDRAM的内部是一个存储阵列,你可以把它想象成一张表格。我们在向这个表格中写入数据的时候,需要先指定一个行(Row),再指定一个列(Column),就可以准确地找到所需要的“单元格”,这就是SDRAM寻址的基本原理。

SDRAM总存储容量 = L-Bank的数量×行数×列数×存储单元的容量

EEPROM

EEPROM(Electrically Erasable Programmable ROM) 是电可擦除存储器。EEPROM 可以重复擦写,它的擦除和写入都是直接使用电路控制,不需要再使用外部设备来擦写。而且可以按字节为单位修

改数据,无需整个芯片擦除。现在主要使用的 ROM 芯片都是 EEPROM

FLASH

flash(Flash Memory)闪存是非易失存储器,掉电不丢失数据,容量大,价格便宜,容量一般比 EEPROM 大得多,且在擦除时,一般以多个字节为单位

FLASH:存储器又称闪存,它结合了ROM和RAM的长处,不仅具备电子可擦除可编程(EEPROM)的性能,还不会断电丢失数据 ,同时可以快速读取数据。,可以对存储器单元块进行擦写和再编程。

NOR FLASH

NORFlash的读取和我们常见的SDRAM的读取是一样,用户可以直接运行装载在NORFLASH里面的代码,采取内存的随机读取技术

所谓“随机存取”,指的是当存储器中的消息被读取或写入时,所需要的时间与这段信息所在的位置无关。相对的,读取或写入顺序访问(Sequential Access)存储设备中的信息时,其所需要的时间与位置就会有关系(如磁带)。

NAND FLASH

NAND 闪存的存储单元则采用串行结构,没有采取内存的随机读取技术,它的读取是以一次读取一块的形式来进行的,存储单元的读写是以页和块为单位来进行(一页包含若干字节,若干页则组成储存块, NAND 的存储块大小为 8 到 32KB ),这种结构最大的优点在于容量可以做得很大,超过 512MB 容量的 NAND 产品相当普遍, NAND 闪存的成本较低,有利于大规模普及。

####PSRAM:伪静态随机存储器

具有类SRAM的接口协议:给出地址、读、写命令,就可以实现存取,不像DRAM需要memory controller来控制内存单元定期数据刷新,因此结口简单;但它的内核是DRAM架构:1T1C一个晶体管一个电容构成存储cell,而传统SRAM需要6T即六个晶体管构成一个存储cell。由此结合,他可以实现类SRAM的接口又可实现较大的存储容量。

FSMC 引脚

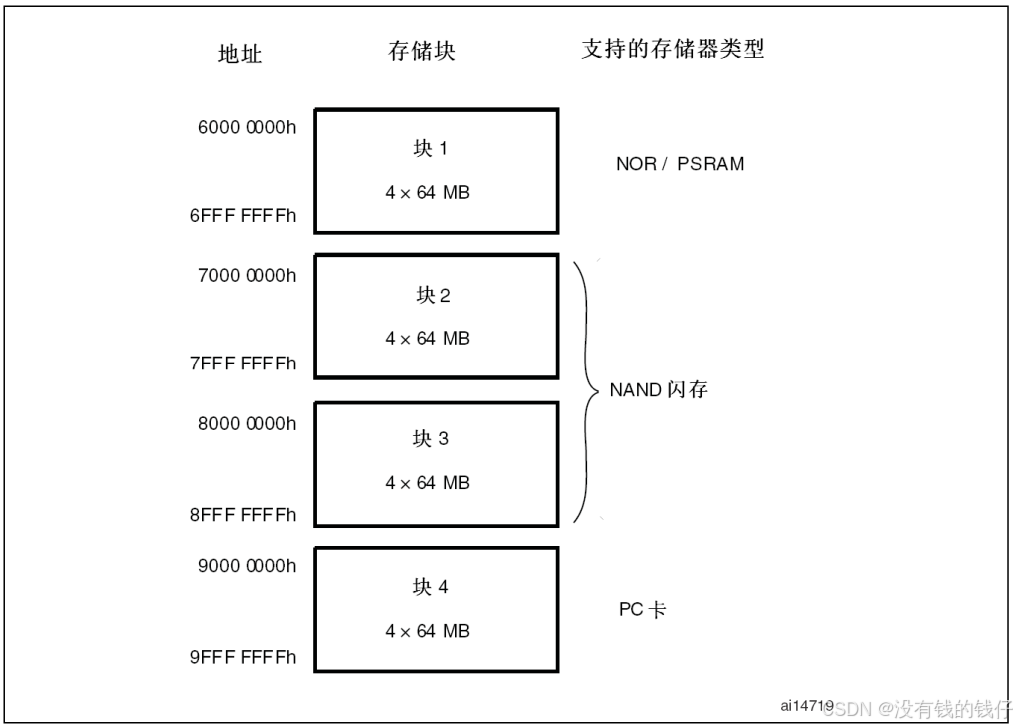

FMC地址映射

FSMC 连接好外部的存储器并初始化后,就可以直接通过访问地址来读写数据 其中这部分在内存中有着固定的存储地址,存储单元是映射到 STM32的内部寻址空间的;

在程序里,定义一个指向这些地址的指针,然后就可以通过指针直接修改该存储单元的内容,FSMC外设会自动完成数据访问过程,读写命令之类的操作不需要程序控制,具体如下:

//FSMC_Bank1_NORSRAM

#define FSMC_Addr_DATA ( ( uint32_t ) 0x60020000 )/*** @brief SRAM写入数据* @param usData :要写入的数据* @retval 无*/ void SRAM_Write_Data ( uint16_t usData )

{* ( __IO uint16_t * ) ( FSMC_Addr_DATA ) = usData;}/*** @brief 从SRAM读取数据* @param 无* @retval 读取到的数据*/ uint16_t SRAM_Read_Data ( void )

{return ( * ( __IO uint16_t * ) ( FSMC_Addr_DATA ) );

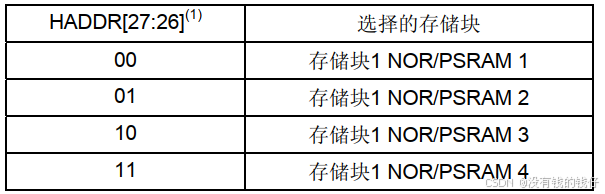

}uint16_t usR=0;usR = SRAM_Read_Data (); /* READ DATA*/FSMC 把整个 存储区域分成了 4 个 Bank 区域,NOR 及 SRAM 存储器只能使用 Bank1 的地址,在每个 Bank 的内部又分成了 4 个小块,每个小块有相应的控制引脚用于连接片选信号FSMC_NE1/2/3/4

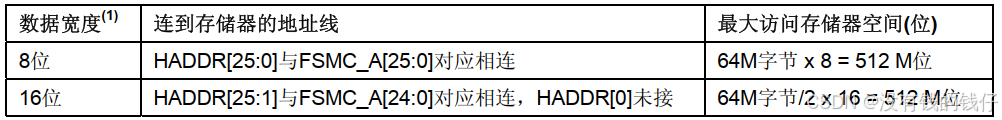

Bank1的256M字节空间由28根地址线(ADDR[27:0])寻址。这里ADDR 是内部AHB地址总线,其中ADDR[25:0]对应外部存储器地址FSMC_A[25:0],而HADDR[26:27]对4个区进行寻址

也就是ADDR 28位地址线的头两位,是选择那个分区,后26位是选择对应64M个byte地址

FSMC时钟

FSMC 外设挂载在 AHB 总线上,时钟信号来自于 HCLK(默认 72MHz),控制器的同步时钟输出就是由它分频得到。

它的时钟频率可通过 FSMC_BTR 寄存器的 CLKDIV 位配置,HCLK 与 FSMC_CLK 的分频系数(CLKDIV),可以为 2~16 分频

它可用于与同步类型的 NOR FLASH 芯片通过FSMC_CLK 引脚输出进行同步通讯,

对于异步类型的存储器,不使用同步时钟信号,所以时钟分频配置不起作用

FSMC 四种模式

对于存储器来说,可以分为带时钟信号的同步存储器和不带时钟信号的异步存储器

同步突发访问中获得第 1 个数据所需要的等待延迟(DATLAT)

异步突发访问方式,FSMC 主要设置 3 个时间参数:地址建立时间(ADDSET)、数据建立时间(DATAST)和地址保持时间(ADDHLD)。

FSMC 外设支持输出多种不同的时序以便于控制不同的存储器, 综合了 SRAM/ROM、PSRAM 和 NOR Flash 产品的信号特点,定义了 ABCD 四种不同的异步时序模型。选用不同的时序模型时,需要设置不同的时序参数

NOE 是存储器的读信号线,N表示低电平有效,O表示output,E表示enable,

NWE 是存储器的写信号线,N表示低电平有效,W表示write,E表示enable,

参考

https://blog.csdn.net/as480133937/article/details/123740365

https://blog.csdn.net/as480133937/article/details/123746123

https://blog.csdn.net/qq_36347513/article/details/122637098

https://blog.csdn.net/call_lkc/article/details/76168485

https://blog.csdn.net/qq_41909909/article/details/107267583