2025.4.29_STM32_看门狗WDG

1.WDG简介

大概意思就是给看门狗设置一个时间范围,在这个范围内必须喂狗(重置定时器),这个操作必须一直执行,比如看门狗的的时间范围是1-2秒,我们就必须间隔1-2秒就喂一次狗,否则它自减到0时就会重置电路,相当于按下reset键。

2.IWDG(独立看门狗)

2.1 IWDG结构框图

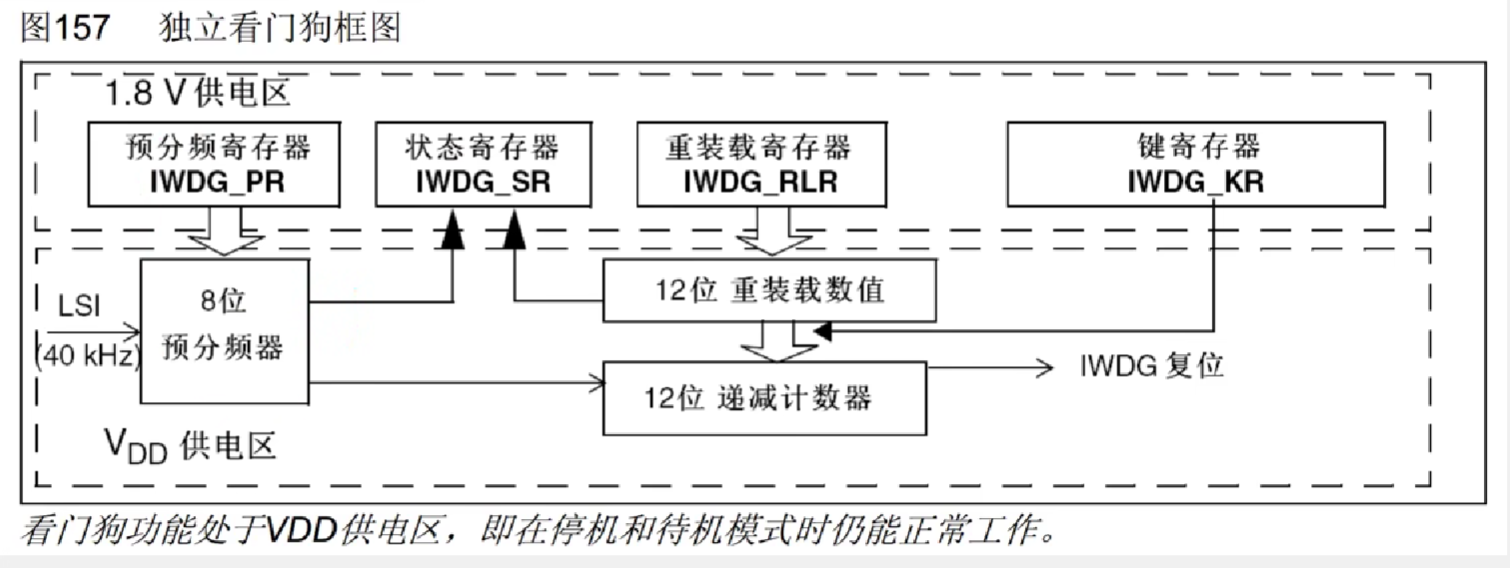

IWDG_PR是看门狗预分频器(Prescaler) ,IWDG_RLR是reload register,相当于定时器的auto reload register。

看门狗由LSI(内部低速时钟)提供时钟,然后接入预分频器,预分频器只有八位,最大只能进行256分频,然后进入十二位的递减计数器,当自减到0时IWDG复位。在正常运行时,我们在键寄存器中写入特定的值控制电路喂狗,喂狗时重装在计数器会写入到递减计数器中,防止递减计数器自减到0产生复位。

上部分的寄存器位于1.8V供电区,下面的看门狗位于VDD供电区。

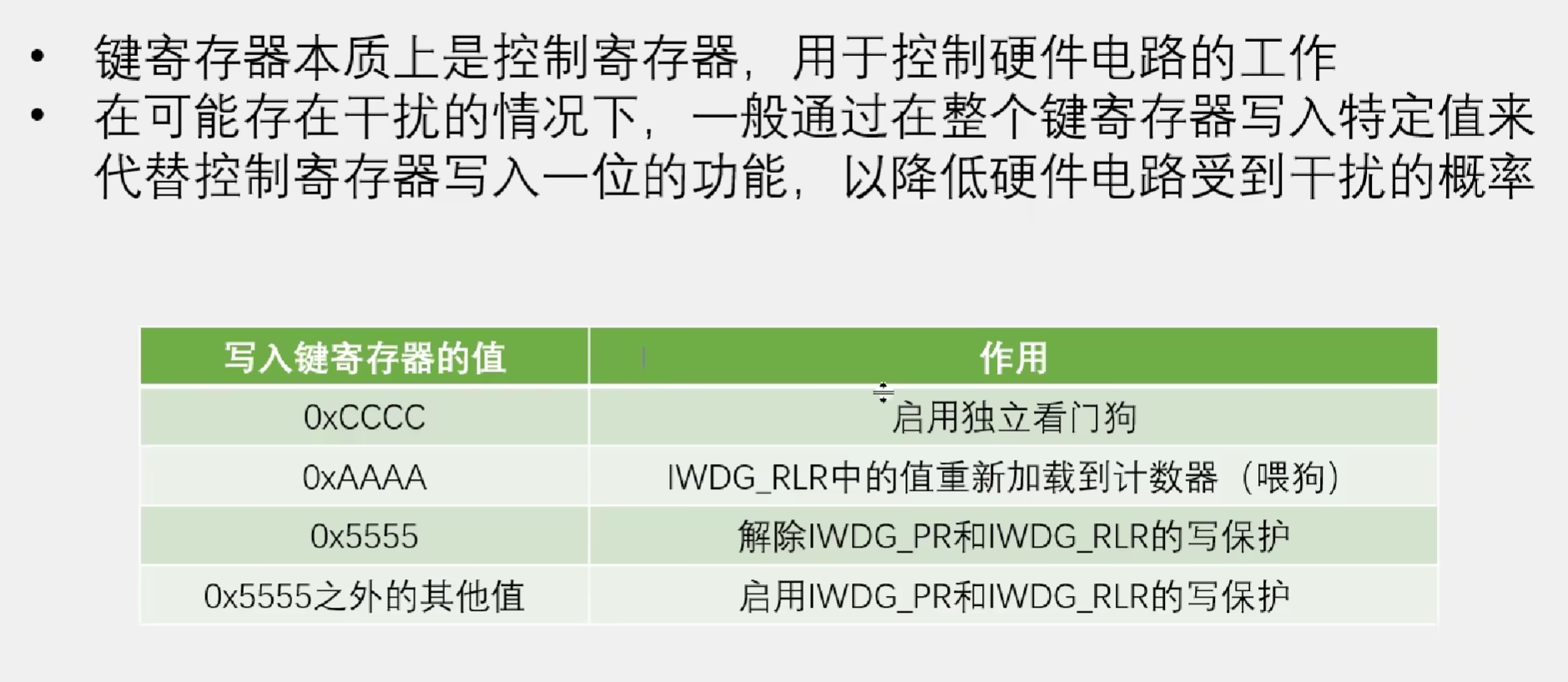

2.2.键寄存器

也就是说,我们想配置看门狗,对他的各个寄存器进行修改的话就必须先配置键寄存器,解除写保护之后才能写入值,写入0x5555之外的其他值都会启用写保护,这样就避免了程序震荡出错导致看门口寄存器被写入错误的值。

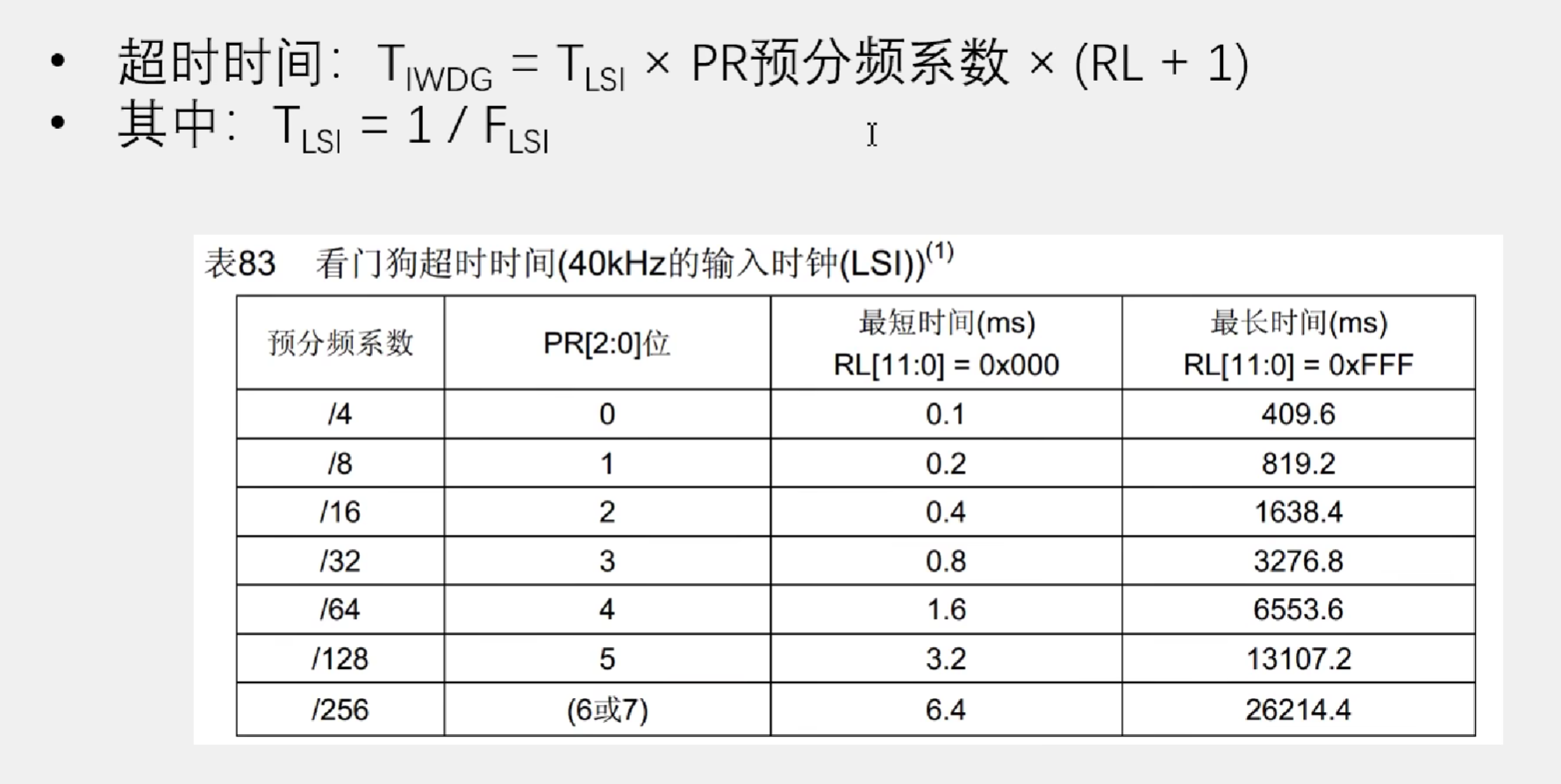

2.3 IWDG超时时间

T(LSI)是内部低速时钟的时间:也就是 1 / 40khz = 0.025ms

PR预分频系数只能从表中选择,不像定时器配置PSC那样可以自己设置一个值

RL+1跟定时器的ARR+1是相同的,都是自动重装值,但是RL只有十二位,所以最大值是4095。所以表里的最长时间是RL=0时求出的;最长时间则是RL=4095时的时间。

3.WWDG(窗口看门狗)

3.1 窗口看门狗框图

![]()

WWDG时钟源是PCLK1(默认36MHz),经过预分频到达递减计数器(也是控制寄存器),窗口看门狗没有重装计数器,我们喂狗的时候直接给递减计数器赋值。上面的看门狗配置寄存器是用来指定最早喂狗时间的,如果递减计数器>配置寄存器(比较器的作用),说明程序喂狗的时间比最早时间还早(比如现在递减计数器是10000,我们设置的最早喂狗时间是5000,说明现在剩余时间还很多,提前喂狗说明程序出错了,也申请复位)。

递减计数器和控制寄存器公用一个寄存器是怎么实现的?这个寄存器一共有7位,我们把低6位作为递减计数器,最高位T6作为溢出寄存器,当T6=1时说明没溢出,T0-T5还没有自减到0,当T6=0时,说明溢出了,T5-T0已经自减到0下一个数,1000000 ---> 0111111,此时说明程序没有喂狗,产生复位。

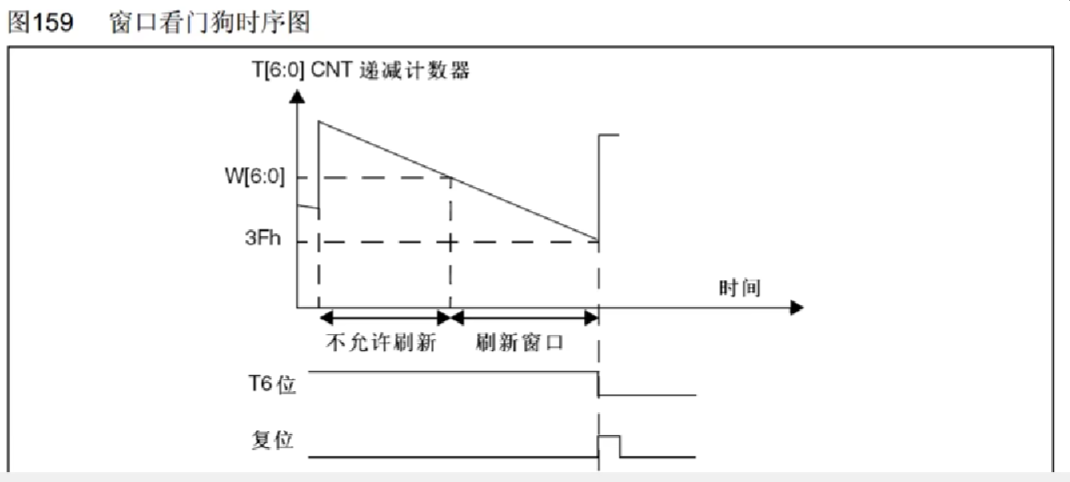

3.2 WWDG工作特性

递减计数器T[6:0]的值小于0x40时,WWDG产生复位

递减计数器T[6:0]在窗口W[6:0]外被重新装载时,WWDG产生复位

递减计数器T[6:0]等于0x40时可以产生早期唤醒中断(EWI),用于重装载计数器以避免WWDG复位

定期写入WWDG CR寄存器(喂狗)以避免WWDG复位

第一条的意思是将整个递减计数器看作一个整体,0x40 = 1 000000,代表递减计数器已经自减到0了,如果此时再减一,控制位就会变为0从而产生复位。

第二条的意思是 比较器比较 现在剩余时间比设定的喂狗时间还大,也就是提前喂狗产生复位。

第三条的意思是可以在递减器=0x40时产生中断,我们称为死前中断。在这个中断中可以保存数据,写入递减计数器避免复位等。

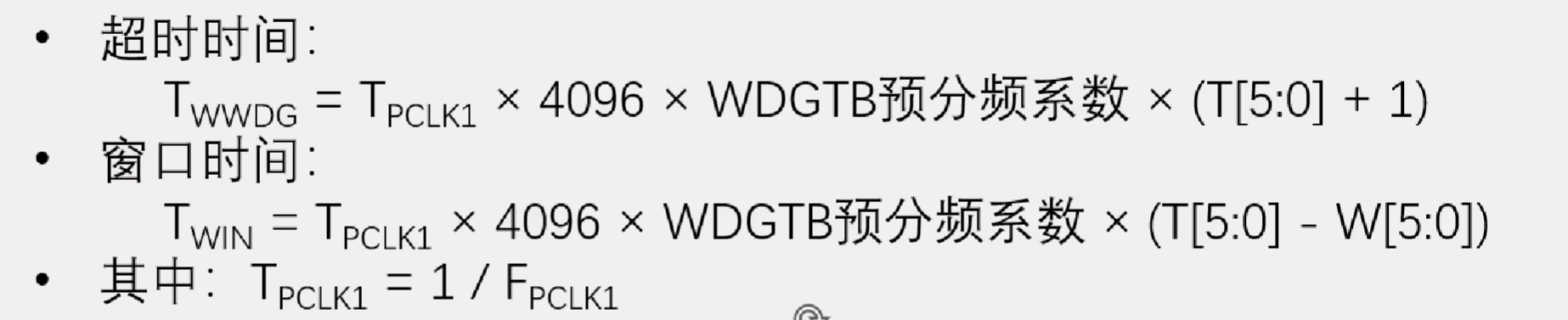

3.3 WWDG超时时间

T(PCLK1) = 1 / 36M。

为什么要*4096?因为PCLK1进入的时候默认进行了4096分频(因为36MHz太快了),独立看门狗只有40kHz。

WDGTB预分频系数 = 2^WDGTB,WDGTB和独立看门狗的PR一样,都是预分频系数。

T[5:0]+1是指递减计数器RLR不包括控制位(最高位)的值。

假设使用7位寄存器(实际常见设计):

WWDG_CR = 0x7F(初始值)

WWDG_CFR = 0x5F(窗口上限)

此时:

过早喂狗区间:0x7F → 0x60(禁止喂狗)

窗口期:0x5F → 0x40(允许喂狗)

超时:0x3F以下(复位)

4.WWDG和IWDG的区别